搜索结果: 1-15 共查到“半导体技术 FPGA”相关记录16条 . 查询时间(0.109 秒)

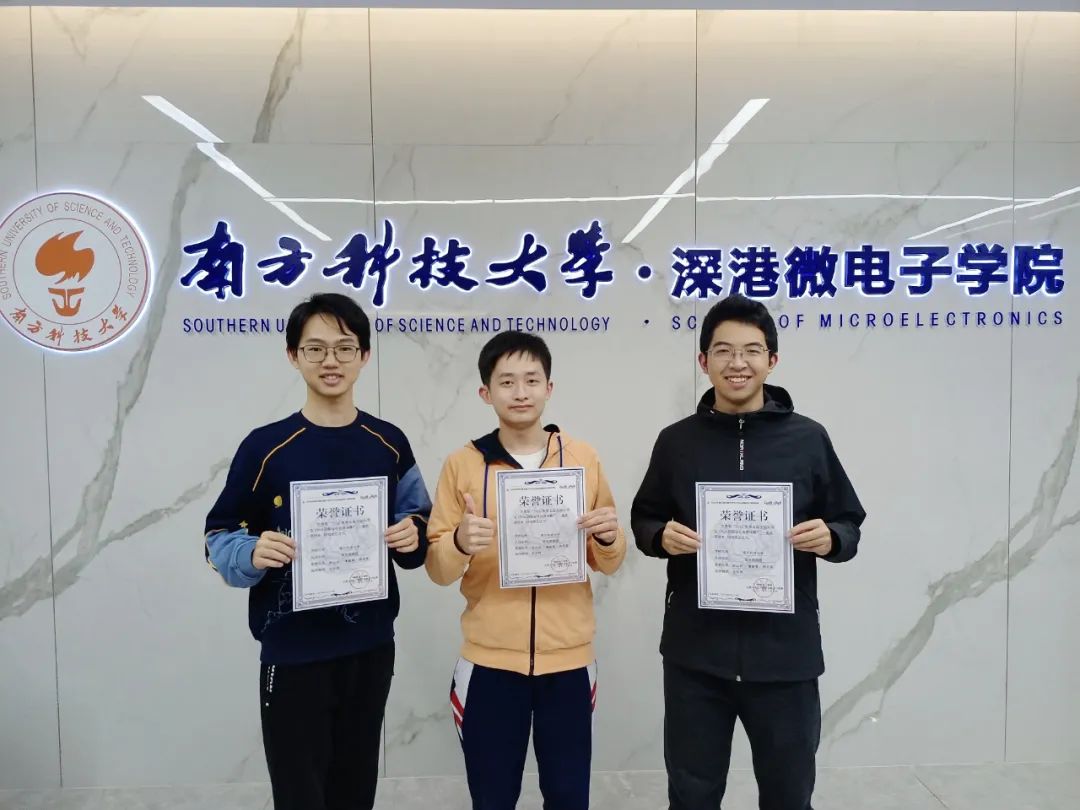

南方科技大学深港微电子学院本科生谭雍昊,陈以非,周名昊荣获全国大学生FPGA创新设计竞赛一等奖(图)

南方科技大学深港微电子学院 谭雍昊 陈以非 周名昊 全国大学生FPGA创新设计竞赛 电路

2022/10/18

VLSI-cell placement technique for Architecture of Field Programmable Gate Array (FPGA) design

Field Programmable Gate Array (FPGA) Space Vector Pulse Width Modulation (SVPWM) Configurable Logic Blocks (CLBs)

2010/1/11

The Field Programmable Gate Array (FPGA) is an on field programmable device which can be designed for different applications. Various types of software are available for its synthesis. The cell placem...

一种基于匹配理论的FPGA三级互连网络测试方法

FPGA 互连网络 匹配理论

2009/9/1

针对FPGA中包含三级可编程开关的互连网络测试,该文提出了一种基于匹配理论的减少配置次数并且与阵列规模无关的测试方法。该方法通过建立结构测试图,按照图的道路长进行分块并应用最小覆盖和最大匹配的原理减少配置次数。对于不同的互连网络结构,与其它方法相比,该方法的配置次数至少减少了10%,并且与阵列规模无关。

基于布线资源图的FPGA互连测试算法

布线资源图 Kruskal算法 静态随机访问内存

2009/8/20

分析基于静态随机访问内存的FPGA开关盒互连资源,提出一种自动生成且与应用无关的测试配置集算法,通过建立布线资源图,根据线网的走向动态设定各边的权重,利用改进的Kruskal算法,自动产生测试配置集。对于FPGA不同的互连结构,该算法对互连资源中的开路和短路故障的覆盖率能够达到100%,且具有测试配置个数少、运行速度快以及与具体硬件结构无关等优点。

FPGA在多进制正交扩频通信系统中的应用

FPGA 扩频通信 多进制正交扩频

2009/8/5

讨论了高速无线分组网络中多进制正交扩频通信系统的设计和实现,其中在系统核心部分的扩频编码调制和解调等很多功能都由FPGA来完成,并对此进行了详细的介绍。

FPGA将逐渐取代ASIC和ASSP

FPGA ASIC ASSP

2009/8/5

可编程逻辑技术目前已经能与ASIC(专用集成电路)和ASSP(专用标准产品)争夺市场,并逐渐呈现出取代ASIC和ASSP的趋势,这极大程度上是因为FPGA技术的发展。FPGA产品在逻辑密度、性能和功能上有了极大的提高,同时器件成本也大幅下降。

介绍了基于Virtex系列FPGA和TMS320C40DSP的可编程通用信号处理背板的设计和制作;并对Virtex系列FPGA的性能和特点进行了分析;同时还叙述了可编程通用信号处理背板的调试;最后给出了背板应用开发实例。

一种低功耗色彩空间转换模块的FPGA实现

CSC 动态功耗 低功耗

2009/7/9

介绍了一种视频压缩系统中使用的色彩空间转换(从RGB到YCbCr)模块的FPGA实现。首先,使用FMC算法实现了色彩空间转换模块,并基于色彩空间转换模块在视频压缩系统中的应用特点提出了一种改进方式,在该方法中使用了少量的单元实现了面积优化和功耗优化。在低采样率的模式下可以减少30%的动态功耗。

一种改进的高速Reed-Solomon译码算法及其FPGA实现

欧几里得算法 高速电路 现场可编程门阵列

2009/5/27

对欧几里得译码算法做了进一步的改进,根据新算法在解关键方程模块中采用了新颖的迭代流水线结构以提高电路工作速度、减小电路面积,设计了高速Reed-Solomon译码器.设计的流水线全并行有限域乘法器,有效解决了传统译码器的速度性能瓶颈.在新的译码器架构基础上,设计了译码器的门级电路,用Xilinx的VirtexII XC2V1000进行了实现和仿真,获得了理想的成果.

针对传统的基于纯硬件平台的FPGA芯片测试方法所存在的种种问题,提出并验证了一种基于软硬件协同技术的FPGA芯片测试方法。该方法引入了软件的灵活性与可观测性等软件技术优势,具有存储深度大、可测I/O管脚数目多、自动完成配置下载(不需人工干预)和自动定位FPGA中的错误等优点,提高了FPGA的测试速度和可靠性,并降低了测试成本,与传统的自动测试仪(ATE)相比有较高的性价比。采用软硬件协同方式针对X...

基于FPGA的RFID数字接收机的设计

相关算法 数字接收机 射频识别

2009/4/27

提出了一种全新的射频识别(RFID)数字接收机的实现方案。针对RFID系统实时性的要求,该设计采用简化的相关算法取代数字锁相环结构,快速准确地捕获频率范围在31.2kHz~780.8kHz内的突发信号,并实现接收数据解码。与采用过零检测方案的数字接收机相比,本设计具有更强的抗干扰能力。该数字接收机在Altera Stratix II EP2S60上验证通过,取得了良好的性能。

视频芯片中的OSD核的设计及FPGA的实现

电子技术 屏幕显示控制核 字符 FPGA

2009/2/20

设计了一种数字在屏幕显示(On Screen Display,OSD)控制核。该设计基于图像分层技术,采用多混合结构实现OSD图像的分层混合显示,增强了人机对话功能。存储器资源的组织方式采用改进型的二步索引算法,该算法通过对行字符组和字符的两次索引获得OSD菜单显示所需的字符点阵信息,使得菜单编号存储器中存储的数据得到了精简,在实现相同功能的前提下对片内存储器资源的需求降低大约38%。利用现场可编...